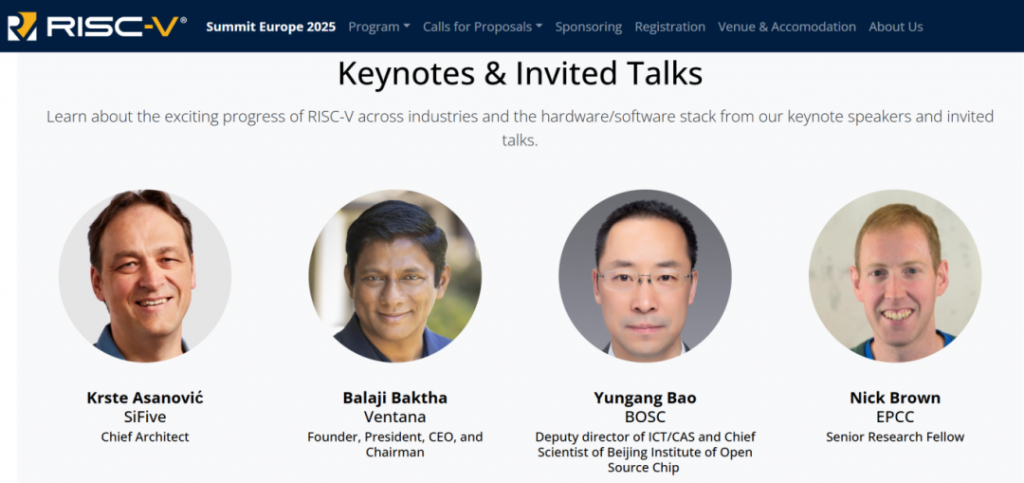

UVHS支持第三代昆明湖16核CPU突破验证挑战,携手探索下一代HPC验证新范式

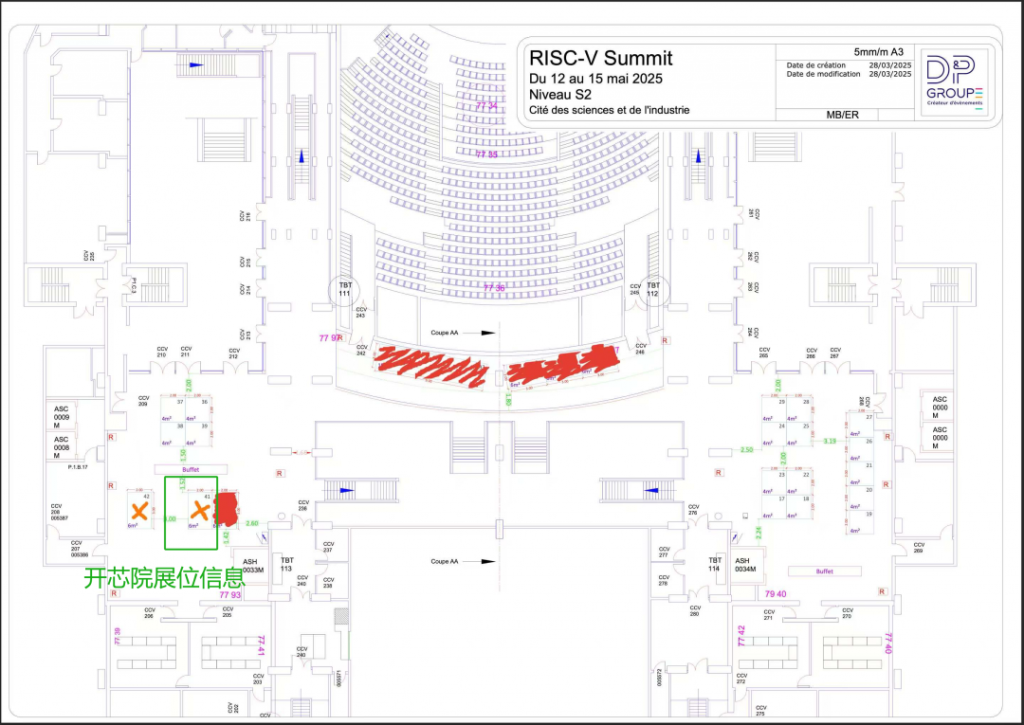

2025年4月9日——北京开源芯片研究院(简称”开芯院”)与中国数字EDA龙头企业上海合见工业软件集团有限公司(简称“合见工软”)宣布双方就“香山”高性能开源RISC-V处理器项目深化技术合作的又一重要成果,依托合见工软自主研发的全场景验证硬件系统UniVista Unified Verification Hardware System(UVHS),双方成功实现“香山”第三代昆明湖架构RISC-V处理器在16核大系统的软硬件协同实测验证。此次技术突破显著提升了处理器的开发验证效率,为后续产品迭代创新提速奠定重要基础。

关键技术突破:16核系统实测性能超10MHz

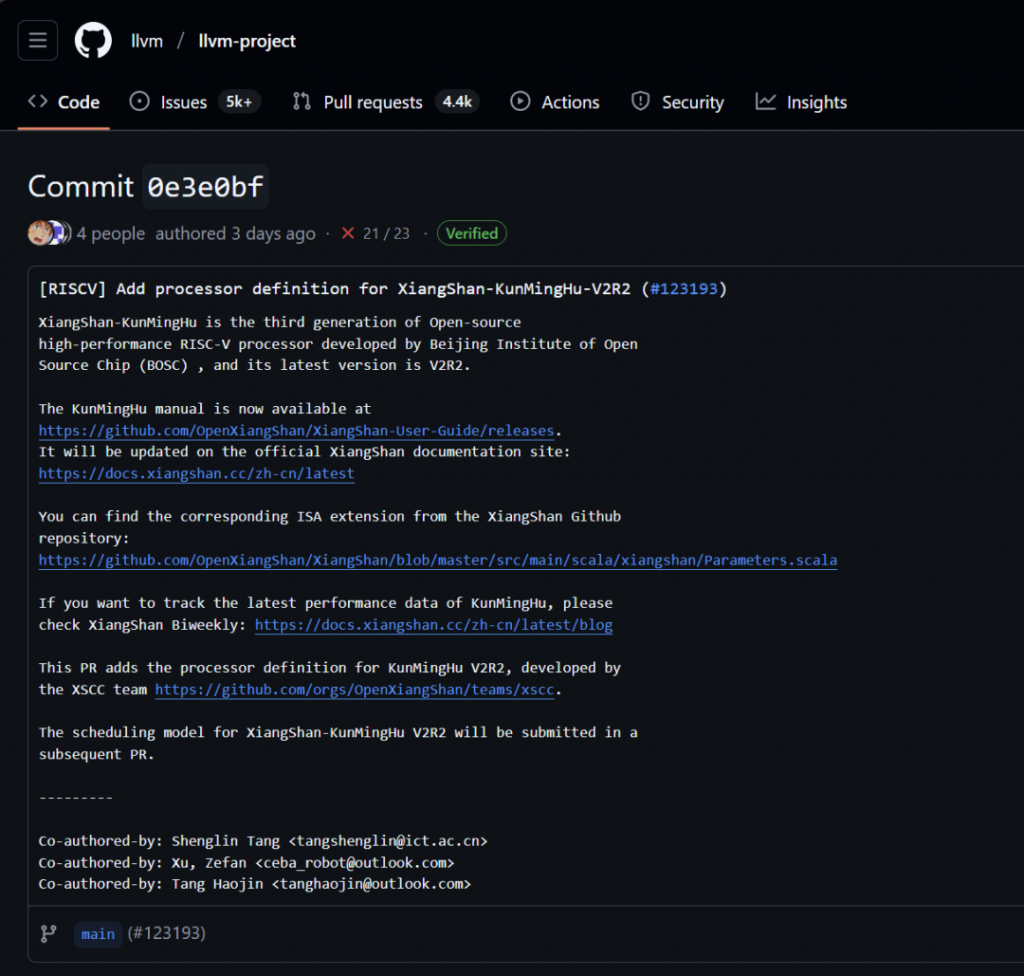

继双方2024年”香山”第二代南湖架构验证项目后的技术成果发布之后,本次合作成果的发布标志着双方携手探索大型处理器验证技术突破的再次升级。在本项目中,开芯院基于第三代昆明湖架构构建的16核RISC-V处理器系统(含总线及存储子系统),通过合见工软5台UVHS硬件平台组成大规模级联原型平台。借助合见UVHS Compiler的智能分割技术,该设计被高效部署至20片AMD VU19P FPGA阵列,实测运行频率达10.2MHz,并充分证明了以下核心优势:

资源优化能力:集成自研UVSyn综合工具,相较传统第三方综合器减少了12%的FPGA资源;

编译效率跃升:全流程编译周期压缩至21小时;

跨平台兼容性:通过自动化的时钟重构、存储模型优化等技术,设计迁移周期从月级缩短至周级;

多核协同验证:开发支持16核/8核/4核多版本兼容的boardfile系统,构建跨版本验证矩阵;

动态加载技术:DDR4后门写入方案,大幅提升内核加载速度。

“RISC-V的创新发展对CPU国产化有重要战略意义,开芯院香山处理器是RISC-V性能的重要标杆,第三代昆明湖架构对标Arm Neoverse N2内核,相较南湖架构显著提升了面向高性能计算与AI场景的复杂度。其增强的并行处理能力、多核协同效率及多级缓存一致性协议,对验证平台提出了近乎严苛的要求。”开芯院副院长唐丹博士指出,“UVHS大规模级联原型平台通过自动分割技术重构了开发范式。过去受限于传统原型验证平台可支持的规模,我们不得不裁剪多核设计,导致系统级验证覆盖率与软硬件协同效率受限。如今借助20片FPGA级联方案,首次实现了昆明湖16核系统的全场景验证——完整保留缓存一致性协议与总线拓扑,在超过10MHz高性能下同步验证Linux调度优化、多核负载均衡等复杂场景,测试深度和广度都有很大的提升。”

生态共建展望:云验证平台赋能行业未来

对于未来规划,开芯院唐丹强调:“后续温榆河片上网络与昆明湖架构的深度融合,将推动更大规模的32核至百核级众核系统的验证突破。我们将与合见工软合作探索两大生态基石的可能性:一是开源EDA工具链与开放的敏捷流程,系统性降低RISC-V企业验证成本;二是基于大型硬件加速器平台的开源芯片设计栈的云端部署能力。这将推动国产RISC-V生态跨越传统工具链壁垒,加速从技术‘可用性’向产业‘易用性’的跃迁。”

合见工软副总裁吴晓忠指出:“我们非常欣喜的看到UVHS大规模级联原型平台能够帮助开芯院实现多核验证上的突破,此次合作也进一步印证了UVHS平台在超大规模HPC类芯片系统验证领域的领先性。未来,合见工软也将与开芯院合作探索构建包括硬件仿真流程在内的超大规模众核芯片系统的全周期验证解决方案。期待通过技术协同创新,与香山一起共同为RISC-V生态系统贡献生产力工具加速RISC-V生态的产业化进程。”

关于北京开源芯片研究院

近年来,RISC-V快速发展,已经成为当前国际科技竞争的焦点。为提升我国集成电路设计水平,建设与国际开源社区对接的技术平台,北京市和中科院高度重视 RISC-V 发展,组织国内一批行业龙头企业和顶尖科研单位于 2021年12月6日发起成立北京开源芯片研究院。研究院以开源开放凝聚产业发展共识,以协同创新激发应用牵引潜力,着力推进 RISC-V 创新链和产业链的加速融合,加速科技创新成果产业化落地,加快打造全球领先的 RISC-V 产业生态。

关于合见工软

上海合见工业软件集团有限公司(简称“合见工软”)作为自主创新的高性能工业软件及解决方案提供商,以EDA(电子设计自动化,Electronic Design Automation)领域为首先突破方向,致力于帮助半导体芯片企业解决在创新与发展过程中所面临的严峻挑战和关键问题,并成为他们值得信赖的合作伙伴。

了解更多详情

请访问www.univista-isg.com。